Project 2:

FPGA EXPONENTIAL DISTRIBUTION GENERATOR

The FPGA realization of a continuous random variate data generator yielding an exponential distribution is of growing interest, particularly in the field of pharmacological medicine as it can be employed in the modelling of the elimination half-life parameter of various administered drugs.

Find out more and get this Project's GitHub RepositoryHardware

The generator architecture is developed on an Intel Cyclone V SoC, 5CSEMA4U23C6 using a LUT based approach containing pre-calculated 16-bit variate values.

Functional Discription

Exponentially distributed generated data samples for the modelling and simulation of the behavior of systems for applications such as in the pharmaceutical field as mentioned in [21]; require fast, efficient and accurate data generators. The proper modeling and simulation of these systems improves the quality of outcomes of these applications resulting in bettering the quality of life of all who require these systems. The onus of the research presented is to realize a new operational modeling technique and hardware implementation on FPGA for the creation of randomly generated exponentially distributed data samples that gives an improved accuracy performance over the curve fitting piecewise linear approximation CDF inversion method by employing an alternative FPGA memory based approach to maximize the speed and accuracy of samples generated. In the literature survey [21]; McCollum et al [15] initially designed an implementation for FPGA that was capable of yielding an exponential distribution by applying a linear function for approximation stored on ROM. This solution however yielded large mean square errors in the approximated values when compared to the desired exponential PDF. This interpolation based design was also not optimized in terms of resources when storing approximation functions.

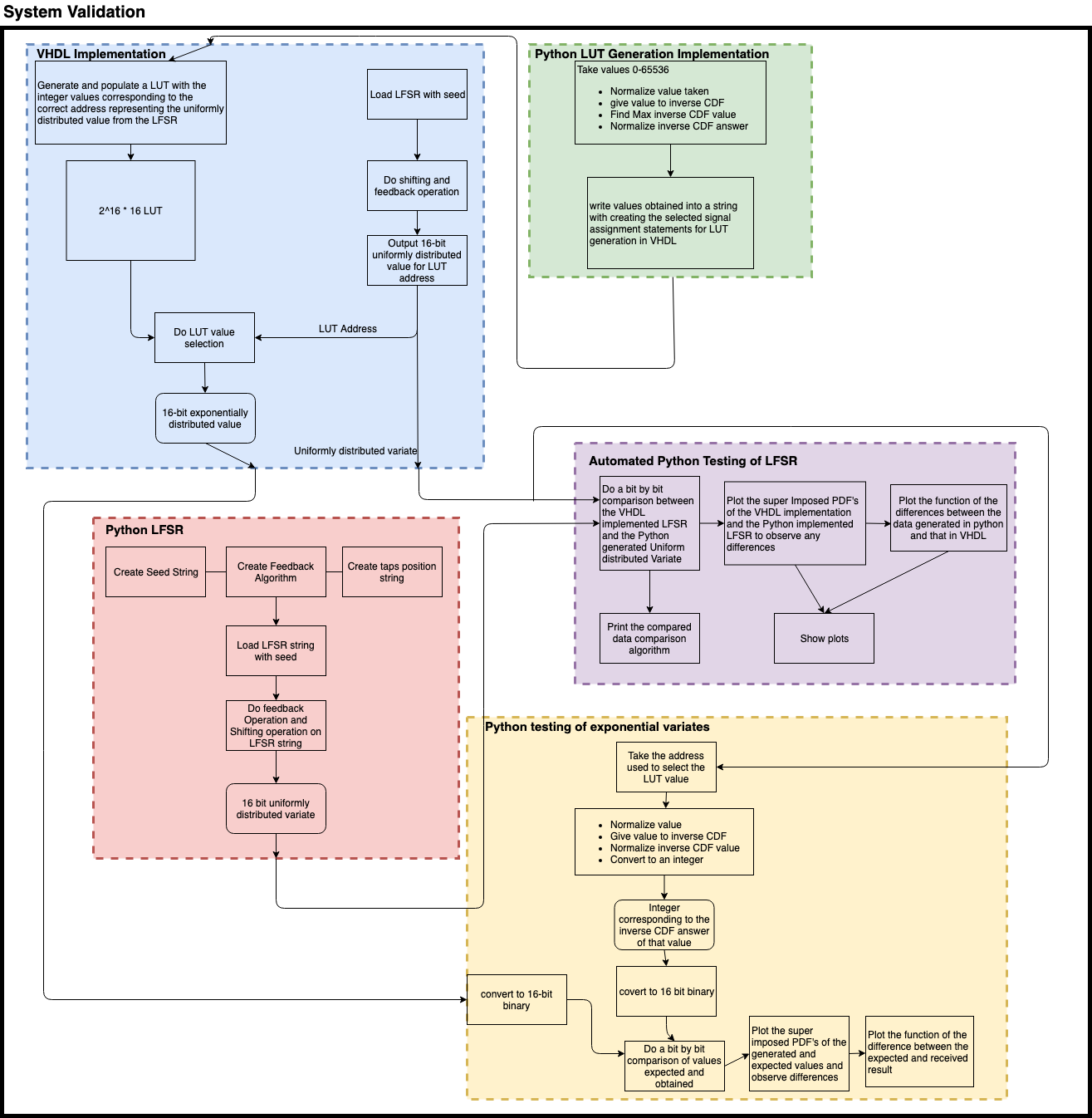

Automated Validtaion

To expand the analyses and verification of data over thousands of iterations for the system, a formal validation of data will be conducted. This validation will take all aspects of the system into account, comparing the results expected and obtained for 10000 samples gener-ated. Formal validation ensure the systems yield the correct output under all circumstances through stress testing of the system over thousand of iterations of sample generation. A python comparison algorithm is implemented for the bit by bit comparison of every sample generated; this allows for automatic checking and validation of the systems operation performance.

A diagram of full system automated validation setup is given below.

Results

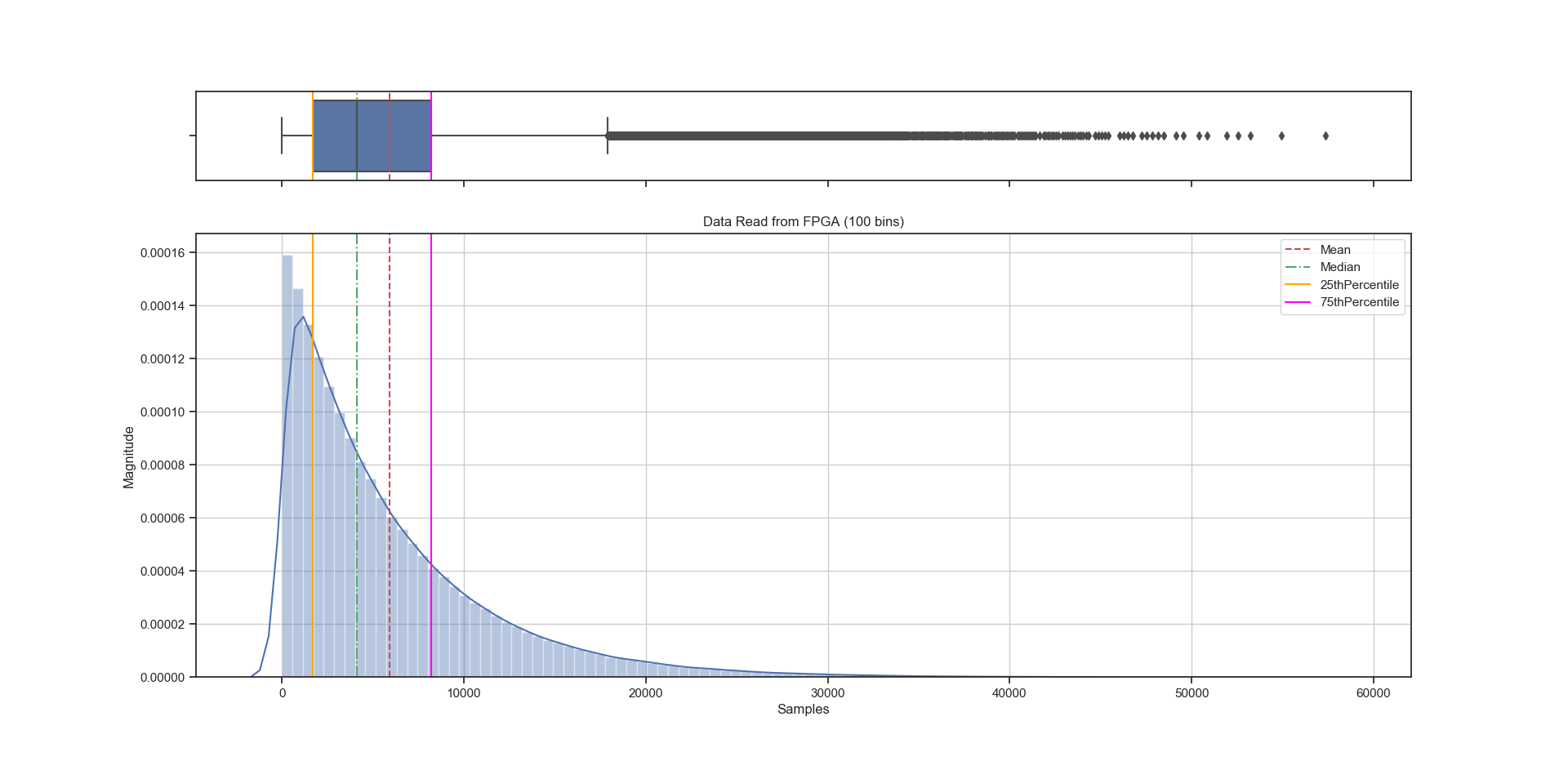

Histogram of the generated FPGA data and its corresponding box plot over 60000 samples with 100 bins

Table of the Summary Statistics yielded for the FPGA and reference data sets

Table of parameters for the goodness-of-fit tests conducted